Tích hợp 3D (ba chiều) đã mở ra khả năng mới cho việc phát triển các mạch tích hợp dày đặc với nhiều thành phần điện tử liên kết hơn. Phương pháp tích hợp 3D cần xếp chồng nhiều lớp mạch điện tử lại với nhau, cuối cùng tạo ra các thiết bị nhỏ gọn và hiệu quả hơn. Các chiến lược sản xuất này có thể giảm kích thước và tiêu thụ năng lượng của sản phẩm điện tử đồng thời nâng cao hiệu suất. Trong các phương pháp tích hợp 3D mới nổi, tích hợp 3D trên một vi mạch đơn (M3D) được coi là đặc biệt hứa hẹn, liên quan đến việc xây dựng các transistor theo lớp trên cùng một nền tảng, thay vì kết hợp các chip đơn lẻ lại với nhau.

(Ảnh nguồn: Nature Electronic)

Theo tin tức từ các phương tiện truyền thông nước ngoài, gần đây, các nhà nghiên cứu từ Đại học Bang Pennsylvania đã thực hiện tích hợp M3D dị thể trên vật liệu 2D, từ đó phát triển ra chip tính toán gần cảm biến rất nhỏ gọn. Nghiên cứu này cho thấy việc sử dụng các chiến lược có thể mở rộng để chế tạo những chip này và những chiến lược này có thể tương thích với quy trình sản xuất hiện có. Bài báo liên quan đã được công bố trên tạp chí Nature Electronics.

Các nhà nghiên cứu cho biết ngành công nghiệp bán dẫn ngày càng nhiều áp dụng tích hợp M3D để thay thế công nghệ lỗ xuyên silicon truyền thống, nhằm tăng mật độ các thành phần điện tử xếp chồng và dị thể. Tích hợp M3D cũng có thể cung cấp phân vùng ở cấp độ transistor và tính dị thể của vật liệu. Tuy nhiên, việc trình diễn quy mô lớn cho tích hợp M3D bằng vật liệu không silicon còn rất hiếm.

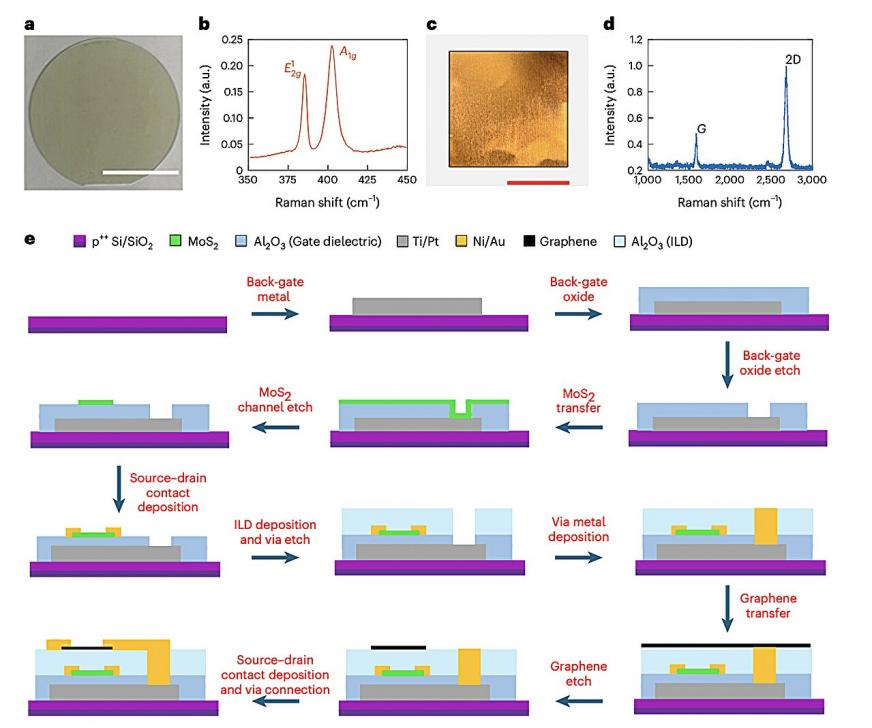

Như một phần của nghiên cứu gần đây, Subir Ghosh và Yikai Zheng cùng các cộng sự đã áp dụng chiến lược tích hợp M3D, dựa trên các thiết bị điện tử 2D để phát triển chip tính toán cảm biến và gần cảm biến. Chip được tạo ra tích hợp hơn 500 transistor hóa học và hơn 500 transistor nhớ, với kích thước lỗ xuyên (vias) 3μm và cách nhau 1μm.

Các nhà nghiên cứu cho biết: “Chúng tôi báo cáo việc sử dụng cấu trúc lỗ xuyên dày đặc (inter-via structure) để thực hiện tích hợp M3D dị thể vật liệu 2D, với mật độ liên kết (I/O) đạt 62500 I/O trên mỗi mm vuông. Chồng M3D này bao gồm cảm biến hóa học dựa trên graphene ở lớp thứ 2, và mạch lập trình dựa trên transistor nhớ MoS2 ở lớp thứ 1, với mỗi lớp có hơn 500 thiết bị. Quy trình này có thể giảm độ gần gũi vật lý giữa cảm biến và các thành phần tính toán xuống còn 50 nm, từ đó giảm độ trễ trong các ứng dụng tính toán gần cảm biến.”

Một trong những lợi thế chính của phương pháp tích hợp M3D là toàn bộ quy trình sản xuất diễn ra dưới 200°C. Do đó, nó có thể tương thích với quy trình tích hợp phía sau hiện đang sử dụng để chế tạo các thiết bị bán dẫn.

Như một phần của nghiên cứu, các nhà nghiên cứu đã sử dụng chip tính toán đã phát triển để thực hiện mã hóa hóa học. Cụ thể, họ đã phát triển một hệ thống cảnh báo, có thể sử dụng để nhận diện và phân loại các chất hóa học khác nhau. Nhóm nghiên cứu đã cho các transistor hóa học trong chip tiếp xúc với các dung dịch đường ở các nồng độ khác nhau và ghi lại tín hiệu điện mà chúng tạo ra từ các dung dịch đó. Sau đó, transistor nhớ xử lý tín hiệu do các transistor hóa học tạo ra và chuyển đổi chúng thành mã số tương tự và số.

Kết quả trình diễn hệ thống cảnh báo của nhóm nghiên cứu làm nổi bật tiềm năng của chip tính toán gần cảm biến mới cho việc xử lý và phân loại các chất hóa học. Trong tương lai, phương pháp sản xuất được đề xuất có khả năng mở rộng quy mô, nhằm phát triển các chip với nhiều mạch và cảm biến hơn, giải quyết các nhiệm vụ phân loại cao cấp hơn.